### **Lecture Notes**

for

### **Sequential Logic Circuits**

(PHYS4008: Electronics)

#### Dr. Pawan Kumar

(Assistant Professor)

Department of Physics

Mahatma Gandhi Central University

Motihari-845401, Bihar

Sequential Logic \* In sequential legic, the outputs are determined not only by the current inputs but also by the sequence of inputs that led to the convent State. In other words, the circuit has the characterister of memory. \* Among the most important groups of sequentia logic elements are various forms of multi-Vibrators. These circuitys can be divided into three types. 1. Bistables: have two stable states e. Monostables: have one stable and one metastable state. 3. Astables: which have no stable states \* The most widely used class of multivibrator is the bistable. These devices can be divided into \* latches \* edge - toiggered flip- \$lops \* pulse - triggered (mouster-slave) flip-flups. \* Each class of bistable may be divided into a range of devices with different operation characteristics. These are often described by Symbolic names such as R-S, J-K, D or T-type devices \* Bistables are frequently used in groups to form registers or counters. \* Registers from the basis of computer memories and also used for serial to parallel convension. Counters are used extensively for timing and sequencing functions. It is of two types 1) Asynchronous or ripple counters 1) Synchronous counters.

3

\* Asynchronous or ripple counters in which the clock for one stage is generated from the output of the previous stage. The result is a ripple effect as each stage changes in require

\* Synchronous counters in which all stages are clocked simultaneously so that all the outputs change at the same time.

\* Both techniques can be used to produce counters that can count up or down.

### Regenerative suitching circuit.

Do Do P

of the output of first inventer Q is equal to 1, this signed is fed to the input of the second inverter, making its output p equal to 0. This in turn forms the input to the first inventer, which makes its output 1. Thus, the circuit is stable with Q=1 and P=0. Alternatively, if Q is equal to 0. this corresponds to a stable state with Q=0 and p=1.

The circuit therefore has two stable states. It elso has outputs I and p where P = Q. It is considered to be a form of bistable multivistrator. However, it is of little practical importance because its state is stable untill power is removed.

guitthing.

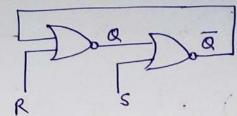

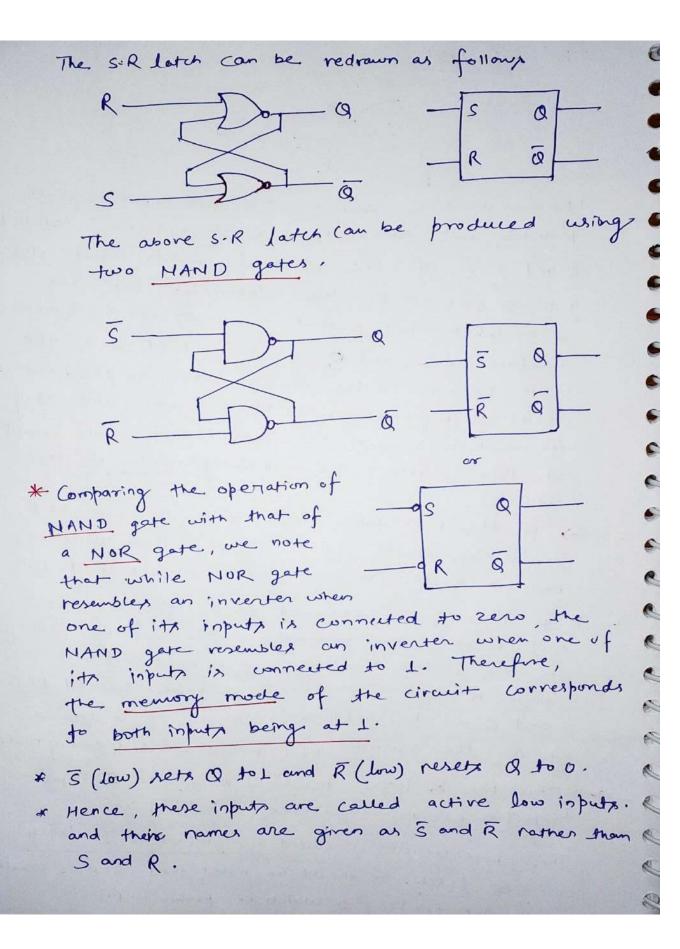

We now have a circuit with two input signals.

Rand S, and two outputs which are now labelled

Rand Q. 9f one input of a two input NOR

gate is held at 0, the relationship beth the

other input and output is that of an inverter.

Therefore, if R and S are both held at 0, the

circuit behaves in the same manner as the previous

circuit of regenerative suitching and will stay

in whichever state it finds itself. We would

call this situation the memory mode of the

circuit.

of the Rix taken to I while S remain at 0, Q will be reset to zero regardless of its previous 8 tate. In turn, this will set Q to 1.

of now R is returned to 0, the circuit will reenter the memory mode and will stay in this state. Similarly, if S is towen to I while R remains at 0, & will be cleared to 9 and Q will be set to 1. Again, if S setums to 0, the circuit will retenter its memory mode to 0, the circuit will retenter its memory mode

"sets" Q to 1, while other inputizato.

The above circuit ix called a SET-RESET latch or S-R latch. 9+ should be noted that S=R=1 result, in both outputs being o which is probibited.

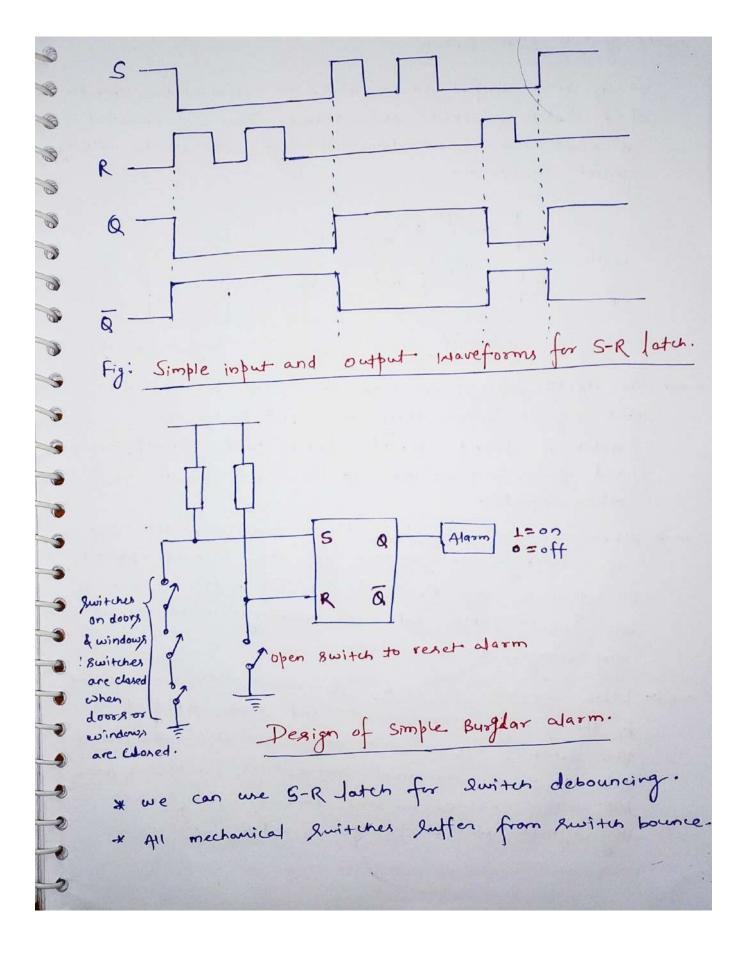

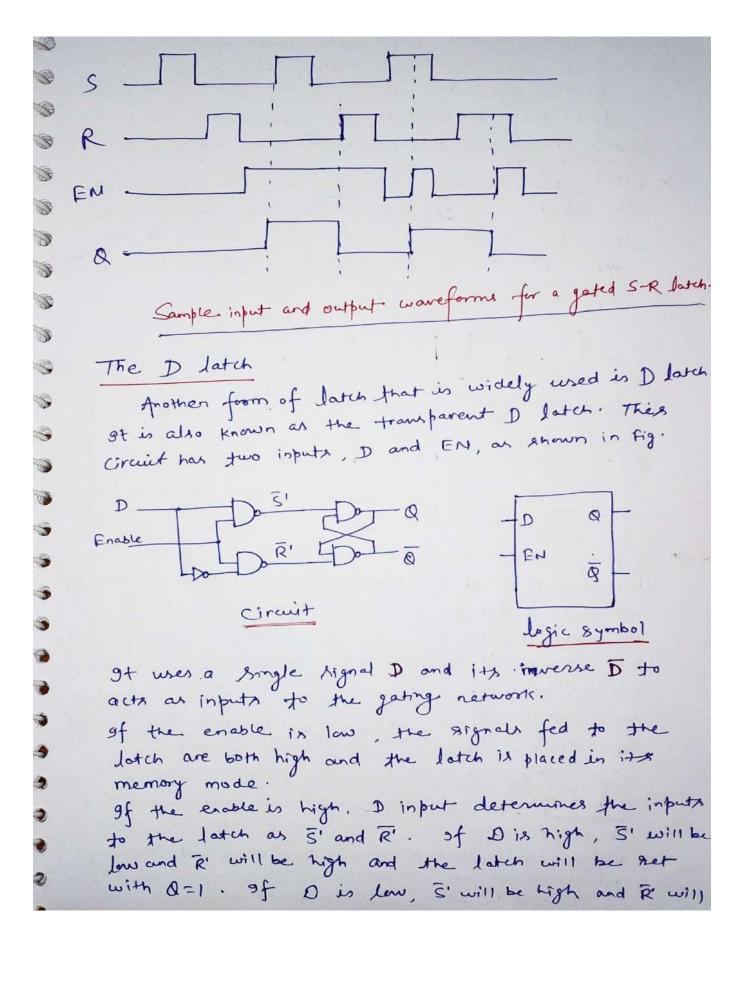

# The gated S-R laten

of a latch so that the inputs can be enabled of a some times and disabled at others. The followings circuit can do it.

0

- input signeds before they are applied to the latch. A third input, latch enable (EN), can be used to allow or inhibits the actions of the other inputs.

- when enable signed is low, the signals \$1 & R' are both high, regardless of the signals applied to the S and R inputs. This puts the active low input latch into its memory made, preventing any change to its. States.

- by the gating arrangement and then applied to the latch. Thus, when enable is high, the circuit acts as a conventional active high input S-R latch, but when enable is low, the circuit ignores any lignals applied to the S and R inputs.

be low, which will reset the latch with Q=0.

Thus, when the enable is high, the Q output the present value, of D, but when enable is low, the Q output will remain in its present land hold gate.

It when the enable is high, the Q output follows the input date D, but when the enable goes low, then output remember the value of D.

The operation of D. latch is illustrated in following figure.

Sample input and output wanteforms for a D latch

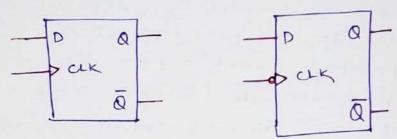

In many situation it is necessary to synchronize the operation of a number of different circuits and it is useful to be able to control precisely when a circuit will change state. Some bistables are constructed so that they only change state on the application of a trigger signal. This is defined as the sixing or falling edge of an input signal called the clock. These devices are termed as edge - triggered bistables or more commonly flip-flops. These are divided into those that are, triggered by the sixing edge of the clock signal (so-called positive edge triggered devices) and those that are triggered on the falling edge of clock (negative edge-triggered devices)

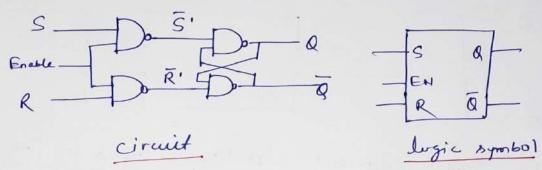

Flip-flops are available in a number of different forms, including the S-R flip-flop and D flip-flop which are edge-triggered versions of the latches discussed earlier.

The circuit symbols used for these circuits are smilar to those of corresponding latchexcept that the enable Input is replaced with a clock input is conventionally indicated by a triangle, while an inverting circle is used to show negative edge-triggered device.

positive edge triggered

B

-

-

-

Negative edge toiggered

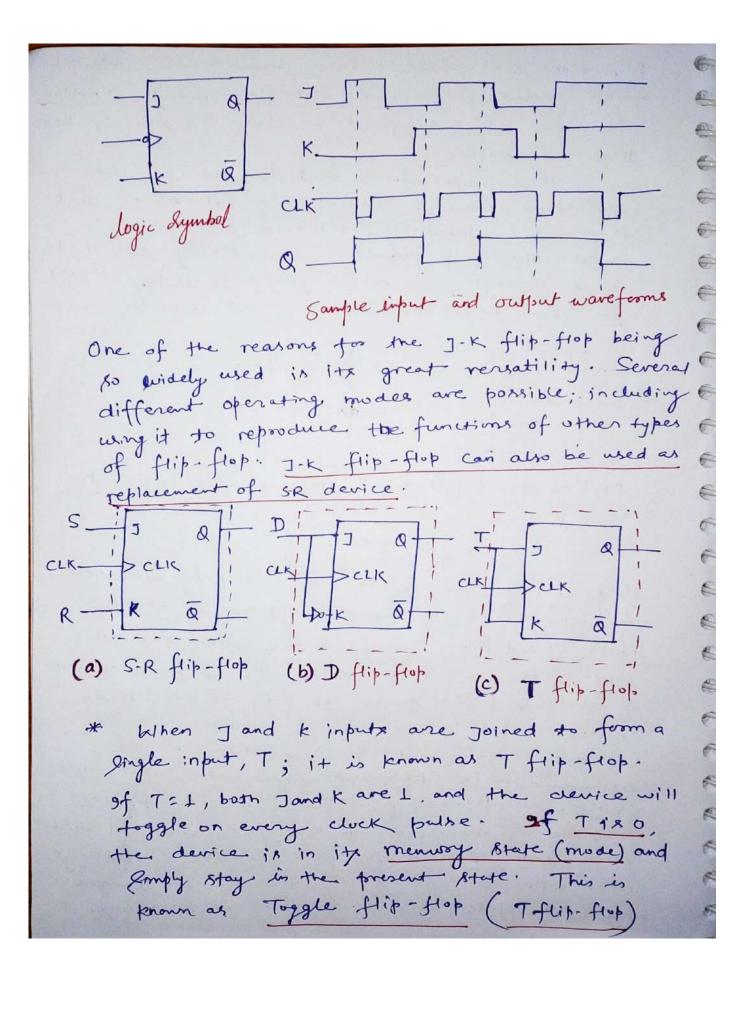

# · J-K flip-flop

of bistable. As its name, suggests, it has two inputs, I and K. Taking I to I while k is at 0 sets Q to I, whereas taking k to I while I is at 0 reset Q to 0. As in the S-R device, when neither input is active, the circuit is in its memory state, but the aperation of the arrangement is different when both inputs are active simultaneously. This is the ambiguous lituation in the case of S-R bistable and so it is avoided. But in the case of the I-K device, when both inputs are active, the circuit changes state (or toggles) when a togger event occurs.

Asynchronous Inputs → We have seen that in flip-flops, the control inputs (for example, the jand K inputs in a J-K flip-flup) affect the operation of the circuit only at the moment of an appropriate transition of the check signal (CLK). We therefore refer to these inputs as Synchronous; because their operation is synchronized to the clock input. In many applications, it is advantageous to be able to get or clear the output at other times, independently of the clock. Therefore, some devices have additional inputs to perform these functions. These are fermed as asynchronous inputs as they are not bound by the State of the clock. However, Il manufacturers are unable to agree on common names for these inputs; so they may be called PRESET and CLEAR, DC SET and DC CLEAR, SET and RESET or DIRECT SET and DIRECT RESET. Here, we use the names PRESET (PRE) and CLEAR (CLR). As with control input these lines can be active high or active low, although more than not they are active low. Fig: Logic Lymbol of J-K flip-frop with PRESET and CLEAR

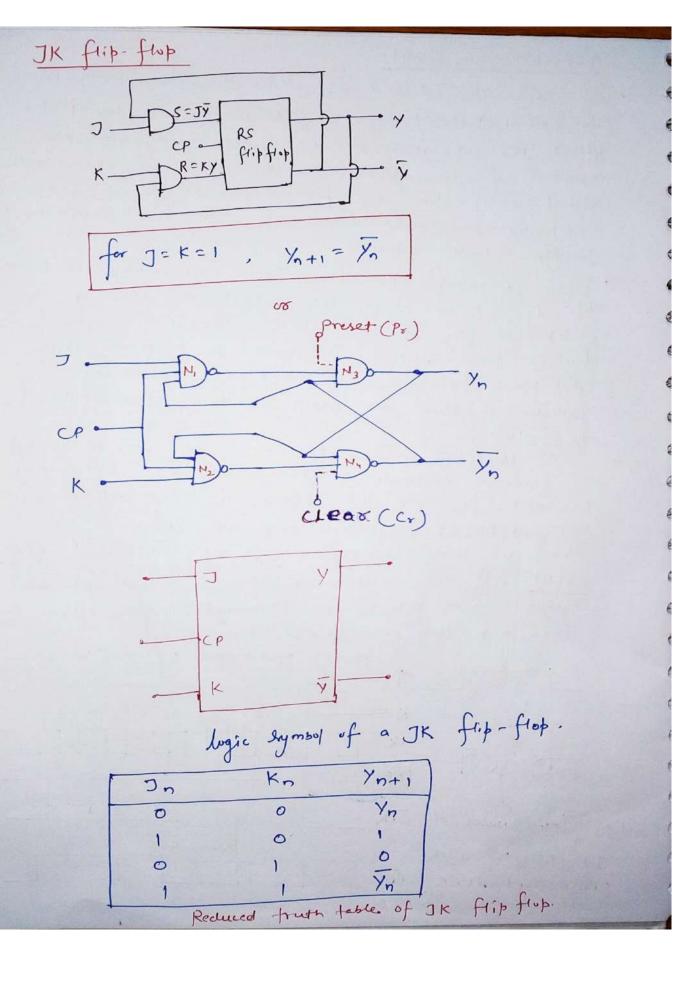

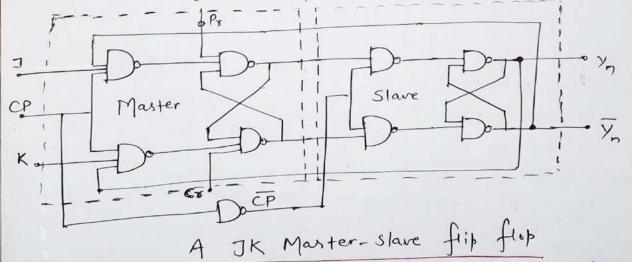

### Master-Slave JK Flip-flop.

9t is a cascade of two RS flip flops where the output of the sewond, called the slave, is fedback to the input of the first, called the master. Positive clock pulses are applied directly to the master and the same after inversion are applied to the slave. The master is enabled when  $P_s = 1$ ,  $C_r = 1$  and  $C_p = 1$ . Since  $C_p = 0$ , the slave is inhibited and so cannot change state. Thus, the  $Y_n$  remains invariant during the time  $t_p$ . Consequently, the race-around condition does not occur.

In Ithen CP=0, the matter is intribited and the slave is enabled since CP=1. The slave is RS flip flop. When  $S=Y_m=1$  and  $R=Y_m=0$ , then Y=1 and Y=0. Similarly, when  $S=X_m=0$  and  $R=Y_m=1$  then Y=0 and Y=1. That is, the value of  $Y_m$  is transmitted to the output Y in the time interval between the clock pulses.

\* 5t may seem that this arrangement would suffer from 'race' problem. Julhen the cluck gues high, the marter's output might change just as the slave is being disabled. In fact, this is not the case. 9t is designed such that the circuit ensures that the delay produced by mester latch is greater than that of inverter used for clock bulse. Registers

A register consists of a group of flip-flops that can store binary information. Since a flip-flop can store. I bit of information, an n-bit word register requires n number of flip-flops connected in cascade, i.e. the output of one flip-flop is the input of the following, and so on. Besides the flip-flops, a register also contain additional gates to execute the data processing operations.

The binary information of a register can be shifted either to the sight or to the left. It is thus commonly known as shift register. A common chur pulse applied to all the flip-flops causes the shift from one stage to next synchronously.

The shifting in or snifting out of data can be carried out through serial shifting and parallel shifting. In serial shifting data bits are allowed to move through the register from one bit to the next in succession. Here the data enter the register at one extreme end (either LSB or MSB) and leave it at the other.

\* In parallel shifting, the data are made to enter or leave involving all the bits simultaneously. Parallel shifting process is faster than serial shifting.

\* parallel shifting are mostly used in digital computers.

Depending on the mode of data shifting, a shift register can be classified into four types.

i) Serial-in serial-out

ii) Serial-in parallel-out

iii) Parallel-in Serial-out

iv) parallel-in parallel-out

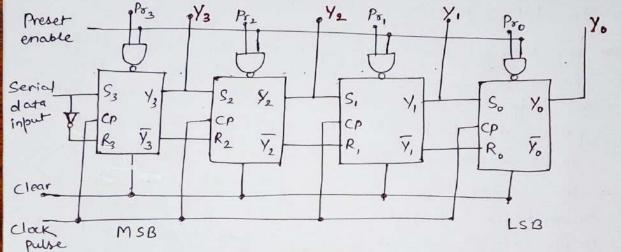

We will consider the operation of 4-bit register of serial-in parallel-out type as shown in Fig.

> Each flip-flop is of the SR (or IK) master place type.

e

⇒ The stage which stores the most significant bit (MSB) is transformed into a D-type latch by connecting an inverter between S and R.

=> The binary serial data, say, 1011 (LSB), 18 to be entered into the register via the Sterminal

A 4-bit shift register

To start with, the flip-flops are cleared by applying a clear (Cr) input so that every output yo, Y, Yafy is 0. Then set Cr=Pr=1 (by maintaining the preset enable ato). The serial data train and the clock pulse are now switched on. The LSB which is I here, is entered into Ff3 when clock pulse (CP) assumes a 1 from a 0 by the action of a D-type flip-flop. Thus after clock pulse, Y3=1 and Y2=Y1=Y0=0.

of y3 is shifted to the master latch of FF2 by the operation of an SR flip flop. At the same time, the next bit I enters the master of FF3. At the end of 2nd clock pulse, the bit in each master shifts to

its slave and results in Y3=1, Y2=1 and Y1= Y0=0. The State of the register after each pulse is shown in

following table.

3

0

V

1

-

-

9

10

-

9

3

3

It is evident that after the third clock pulse, Y2 has shifted to Y1, Y3 to Y2, and the third input bit 0 has entered ff3, so that 1/3 = 0. Similarly after the 4th clock pulse, y3 has shifted to Y2, Y2 to Y, and Y, to Yo and 4th input bit I has entered ff3 resulting is y3=1.

Clearly, the input word 1011 has been installed in the register after 4th clock pulse. The clock pulses are stopped after the word is registered. The outputs may be read simultaneously since they are available on reparate lines As the data enter the Eyetem Serially, but come out in parallel, it is called a serial - in parallel - out register. Shift registers are available in Ic form.

| Clock | Serial | Y3              | Ye | Υ, | Yo |

|-------|--------|-----------------|----|----|----|

| pulse | data   | 0               | 0  | 0  | O  |

| 1     | 1-     | 1               | 0  | 0  | 0  |

| 2     | 1      | 1               | 71 | D  | 0  |

| 3     | 6      | > 0_            | 11 | 11 | 0  |

| 4     | 1_     | $\rightarrow 1$ | DO | 31 | TK |

Reading of the shift register after each clock pulse.

## Counters

A counter is a sequential circuit that keeps a reword of a clock pulses sent through it. Like a register, a counter also consists of a group of flip-flops.

However, a counter has a characteristic internal sequence of states through which it passes when a series of clock pulses are fed to it. A register, on the other hand, had no such characteristic sequence the states of a register are controlled by the data applied to it.

The counters are divided into two categories:

- i) ripple (asynchronous) counters

- ii) Synchronous counters

In a sipple counter, all the flip flop donot receive their triggering pulses simultaneously. Here the first flip flop only get the incoming clock pulse. The output of the first flip flop provides the clock pulse for the second flip-flop, the output of the second provides the clock pulse for the third and second provides the clock pulse for the third and so on.

While in a synchronous counter, all the flip flups of the counter receive their triggering pulse simultaneously, since the same clock, pulse input triggers them all

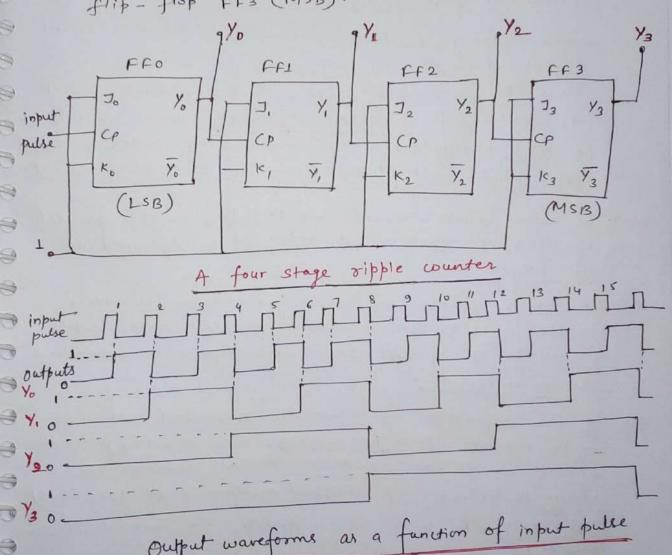

\* Ripple (Asynchronous) Counters: consider a chain of four JK master-slave flip-flops with the output y of each flip-flop providing the clock input of the following flip-flop as shown in fig.

The pulses to be counted are fed to the clock input of the first flip-flop (FFO) which displays the LSB of the binary number. I and k of all the flip flop are tied to the supplys voltage giving J=K=1. Hence the master changes the state each

time the waveform at its clock input rises from 0 to L, and this state of the master is transferred to the slave when the clock input drops from 1 to 0. Thus Yo changes state at the trailing edge of each pulse and any of the other y's suffers a transition only when the output of its previous flip-flop drops from 1 to 0. This type of negative transition (ripples down the counter from the first flip flop FFO (LSB) to the last flip-flop FFO (MSB).

The figure shows that after the passage of first input pulse the output of the counter reads 0001, after the second pulse it reads 0010 and 80 on.

Since there are four flip-flops and the output of each flip-flop has two states (o and 1). the counter has 24 (=16) states. After 16 pulses the counter output shows 0000, i.e. the counter returns to 1th original state. Thus 16 pulses in succession form a cycle.

6

eleasty, a chain of n flip-flops will count states up to 20 (= N, say) before the counter come back to its initial state. Such a chain is called a counter of modulo 20 or N, where modulo (or mod) represents the number of states of counter. The counter is read by means of a decoder circuit.

- The above counter counts input pulses in the forward direction, i.e. from a upwards. It is termed as up counter.

- The above counter can count in reverse direction if the outputs are taken from the complement terminals of all the flip-flops. It is termed as down counter.

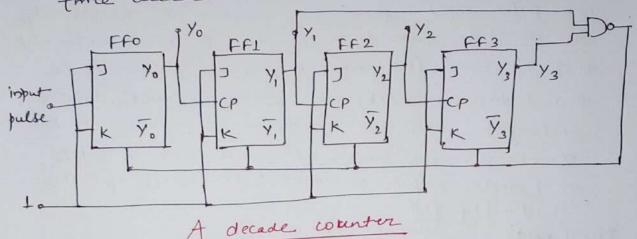

- eycle repeat after 10 states, the resulting circuit becomes a decade counter or mod 10 counter. The binary equivalent of decimal number 10 is 1010 (LSB) and so  $y_0 = 0$ ,  $y_1 = 1$ ,  $y_2 = 0$  and  $y_3 = 1$ . Thus at the count 10, the outputs  $y_1 = 1$  and  $y_3 = 1$ . These two outputs are applied to a NAND gate, the output of which feeds all the clear inputs in parallel as shown in next figure.

Consequently, whenever  $y_1 = y_3 = 1$ , the output of the NAND gates becomes 0, and all the flip-flops reset to 0 after 10 input cycles.

S

of it is required to count 1000 (=103), then three decade counter units are cascaded.

ii) Synchronous Counter: All the flip-flops are clocked simultaneously. Hence propagation delay time is reduced significantly. The other advantage of the eynchronous counter is absence of unwanted eynchronous counter is absence of unwanted spiker at the decoder output because all flip-flops charge states himultaneously.

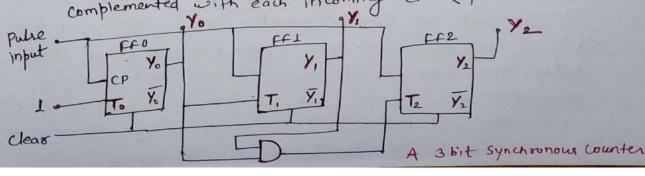

A 3-bit synchronous counter is shown below. Each flip-flop is T-type, formed by connecting the Jand K inputs together of a JK flip-flop. When T=0, there is no change of state of the output when the dock pulse is applied. When T=1 the flip flop is complemented with each incoming clock pulse.

The operation of the counter ctruit shown in figure is explained with reference to the following table which displays the country sequence of a 3bit binary counter over a cycle.

The output  $V_0$  (LSB) Changes state for each clock pulse input. Also, the output  $V_1$  changes only when  $V_0$  drops from I to O. So if  $V_0$  is connected to  $V_0$  of next flip flop,  $V_1$  will alter its state from I to O (or O to I) when  $V_0 = T_1 = I$  and remains unchanged when  $V_0 = T_1 = O$ . Table shows that  $V_0$  changes its state whenever both  $V_1$  and  $V_0$  are  $V_1$  where  $V_2$  changes its state whenever both  $V_1$  and  $V_0$  are  $V_1$  whose output is connected to the  $V_2$  of the

|               |                | wput st | 0  | No of Com   |

|---------------|----------------|---------|----|-------------|

| 1             | y <sub>o</sub> | , 7,    | Y2 | pulse input |

|               | 0              | 0       | 0  | 0           |

|               | 1              | 0       | 0  | 1           |

| ← Counting Se | 0              | 1       | 0  | 2           |

| a 3-bit co    | 1              | 1       | 0  | 3           |

|               | 0              | 0       | 1  | 9           |

|               | 1              | 0       | 1  | 6           |

|               | 0              | 11      | 1  | 2           |

|               |                |         | 1  | +           |

\* 9f the output yo of figure (SIPO shift register) is connected to the serial data input, the shift register is then converted to a circulating memory known as a sing counter. Suppose all the flip-flops are cleared and only fro is preset. This gives  $y_0=1$  f  $y_1=y_2=y_3=0$ . Now with the application of first clock pulse, the state  $y_0$  of fro is transferred to from the safer the first clock pulse  $y_3=1$  and  $y_2=y_1=y_1=0$ . After the 2nd pulse (clock), the bit 1 of  $y_2$  will move to  $y_2$ : i-e.  $y_2=1$  and  $y_3=y_1=y_0=0$ . Therefore, with

every clock pulse input, the state I will more progressively around the ring formed by Y3, Y2, Y1, Yo'

\* Applications: To count the objects by loading them lingle-file on a conveyor best beth a light source and a photoelectric cell. Here, each object, while passing gross light source and photoelectric cell passing across light source and photoelectric cell sproduces an electric signal which is fed to the counter.

#### **References:**

- 1. Digital Fundamentals by Thomas Floyd

- 2. Digital principles and Applications by A. P. Malvino and D. P. Leach

- 3. Modern Digital Electronics by R.P. Jain

- 4. Digital Design by M. Mano

- 5. Electronics Fundamentals and Applications by D. Chattopadhyay and P.C. Rakshit

- 6. Electronic Devices and Circuits by J. Millman and C.C. Halkias

- 7. Integrated Electronics by J. Millman and C.C. Halkias